铁电液晶的失效分析

铁电液晶的失效分析

B. PICART, A. ARRANZ, G。技术与失效分析实验室,BP 27, 33610 Cestas,法国

目前VLSI芯片的复杂性要求强大的工具来检测可能的缺陷。为了达到这个目的,内部非接触测试方法,如电子束或激光测试,已经被开发来帮助精确定位电气缺陷。

本文的目的是描述在IBM COMPEC实验室用于失效分析的液晶测试方法。这些材料的电光特性允许在芯片表面显示电信号。

介绍

随着超大规模集成电路的复杂性和集成度的增加,有必要采用新的电气测试方法来很好地了解这些电路的内部功能。从每个外部引脚获得的信息数量不再充足,测试方法需要越来越好的工作工具。此外,集成电路的物理尺寸正在减小,减少了使用直接接触(机械探针)进行内部测试的可能性。

因此,有必要发展内部非接触测试方法,如电子束和激光测试。考虑到上述因素,IBM COMPEC失效分析实验室与波尔多的Paul Pas- cal研究中心开发了一种铁电液晶(LC)测试方法。它们的光学特性取决于芯片表面的电场;因此,它已经成为可能的可视化路径信息和确定区域的信号是存在的。本文的目的是描述该方法的基本概念,并展示其在集成电路故障分析中缺陷定位的可能应用。

液晶描述

液晶是在晶体相和各向同性相之间显示不同中间相的化学物质。这些混合物既没有显示出晶体固体的方向和位置的顺序,也没有显示出液体方向和位置的混乱。在弱电场作用下,这些流体易变形,光学性质易发生变化。

074&8017/91/04024W6$05 . oo @ 1991 John Wiley & Sons, Ltd。

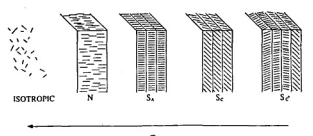

图1所示。各种与温度有关的相

液晶可以采用不同的内观相:各向同性(I)、胆甾相(N*)、向列相(N)或近聚体(SA, SC, SC)(图1)。

这些相变是由温度变化引起的。离开结晶态时,温度的升高导致中间相的有序度越来越低(K-SC*- SA- N-N-1)。

1.铁电SC液晶

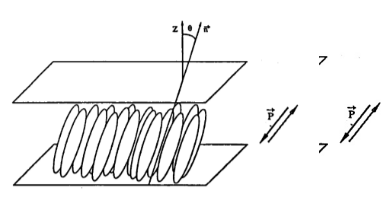

在这种应用中使用的液晶是铁电近晶型的。SC阶段呈现了一个具有平行层的结构。

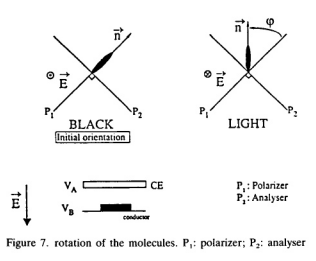

分子与SC层法线的角度为0:可视化的对比将是8值的直接函数(最佳值是8 = 22'5')(图2)。

铁电性和电池尺寸的极限条件保证了液晶的宏观极化P,这将允许它与电场耦合。P表示LC的电场灵敏度。

根据施加的电场方向,如果E值大于阈值(0.1 V/p,m),分子就会旋转。LC分子的初始取向与芯片平行

1991年4月收到

2.近晶C层的结构

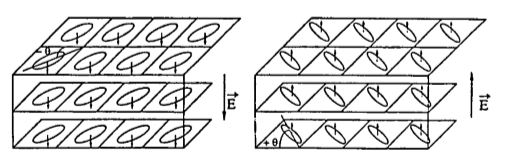

表面上,我们有两个稳定的位置,“向上”和“向下”状态的电场E(图3)。

根据光的偏振方向和分子的取向,我们可以观察到双折射液晶中的光退偏。

在选择近晶C液晶时,需要在响应时间和可视化对比之间做出妥协。

样品制备

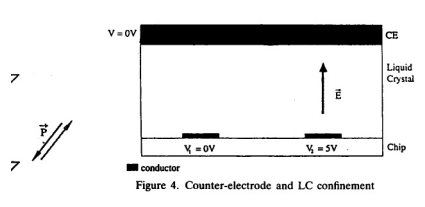

样品的制备要求LC被限制在芯片和名为“反电极”(CE)的导电玻璃板之间(图4)。反电极有两个用途:

(a)将LC的厚度限制在10pm以下

(b)选择我们想要可视化的信号。

为了优化可视化质量,有必要在一个方向上创建分子的初始对准。将试样放入烘箱中,根据要求的条件降低温度,完成对中。我们用研磨机将聚合物薄膜(PVA)雕刻在电极的反电极表面,从而使其具有良好的对准方向。一旦分子以两种稳定状态中的一种排列,并且电场垂直于芯片,分子就会发生旋转。

可视化原理

通过电场的作用,可以改变分子的方向。为了把这两种状态形象化,它充分用偏振光照射芯片,观察反射光穿过偏振器(图5)。根据内部电场方向,LCs充当光开关。

设备

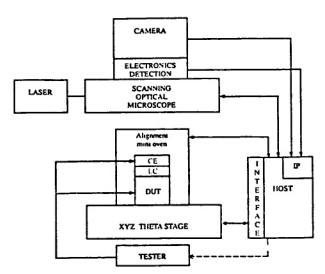

液晶测试装置主要配置如下(图6):

1.带有交叉偏振器和照相机的光学显微镜。对于未来的应用,提高可视化的可观察性是必须的。这将通过图像处理技术来实现,使图像简化并提高其质量。通过这些改进,将实现DFI(动态断层成像)方法。在未来,一个激光扫描显微镜将专门用于空间站和探测模式项目。

2.字发生器,它模拟芯片并允许电进入被观察的芯片区域。

3.样品制备所需的设备。例如,在热处理过程中,为了使LC分子在一个方向上排列,用PVA雕刻CE的研磨机,也使用PC控制的烤箱来准备这个热循环。

液晶测试

Zmaging模式

当一个部件被测试时,导电地被提交到各种动态电位。

图3. 电场的影响

图6. 工作岗位。IP:图像处理接口;DUT:被测设备;LC:液晶;CE:对电极

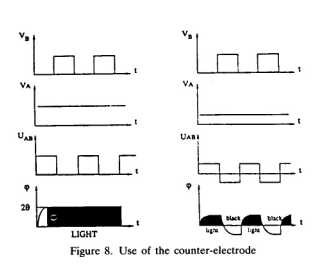

即电路的每个节点都有电场。通过使用反向电极,可以选择我们想要显示的信号(图7和图8)。

如果测试频率高于LC的截止频率,LC只会受到平均电场的影响:这种应用就是“平均场观测”。

当芯片频率低于LC频率时,分子可以随着电场的变化而旋转(图8),LC状态随着信号的传播而变化。在这个阶段,“实时成像”将通过频闪分析来冻结信号。目前我们在IBM COMPEC实验室工作的是“平均现场观察”,测试频率高于LC,直接通过光学显微镜进行观察。其优点是:彩色图像和分辨率好。

在平均电场中可以观察到近晶相和向列相。为了有一个非常好的图像对比度,有必要使一个完美的排列的分子。

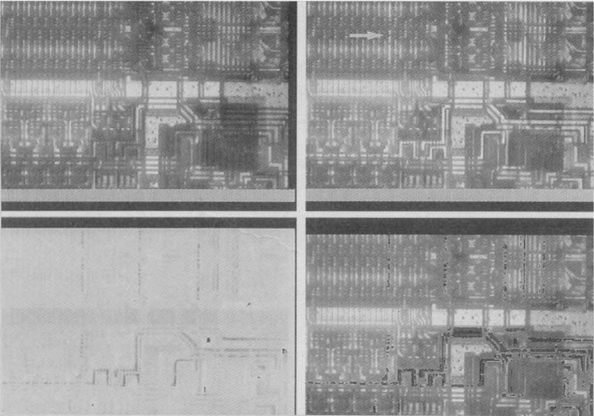

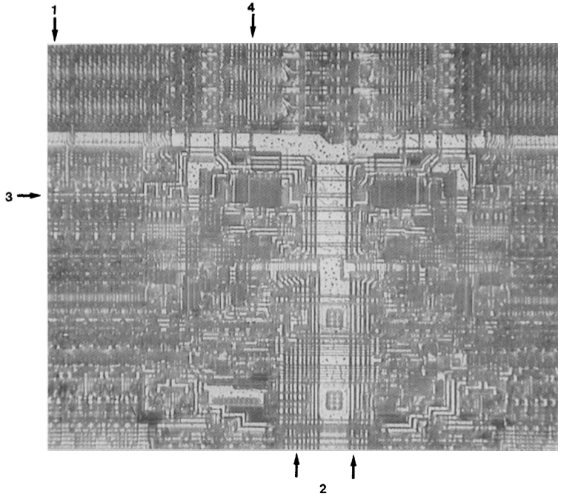

数据总线可视化(图9)。图片显示了使用SC*在64K SRAM上的测试序列中可视化电信号。

你可以在测试前观察样品,当没有电压应用:颜色(这里没有显示)提供了一个非常好的分辨率拓扑的信息(1)(图像a)。

在测试序列期间,数据被写入内存的数组中。有关的信息内部电态用LCs突出显示。因此可以看到数据的传播、列解码器和所选的位线(2)。

![]()

内部电态用LCs突出显示。因此可以看到数据的传播、列解码器和所选的位线(2)。

对A和B图像进行降噪和相减处理后,得到数据路径(3)。

最后一幅图像显示了图像处理的结果和信号传播的可视化(4)。

SRAM 64K通用视图(图10)。我们可以很容易地观察到信号在整个芯片表面的传播。所述数据写入在所述存储器阵列(1)的左侧,可在图(2)的下方看到所述数据总线,并刺激所述列解码器(3)和行解码器(4)。

在“平均场观察”的对比方面,nematics的使用比近晶C给出了更好的结果。在动态电场中,由于nematics的响应时间(1毫秒),使观测变得非常困难。电子邮件有更好的响应时间(1ps),因此提供“实时电子邮件”。

近晶A相位,具有非常好的响应时间(100 ns),将提供进行更高性能的频闪分析的可能性。

在图像处理中,使用LCs的优势是由于图像是真实的颜色。我们可以对这两幅图像进行处理,以便区分它们之间的区别:例如好的部分和有缺陷的部分。这个操作可以让我们看到wb-ich的“线路”发生了变化,即线路有或没有电信号。

探测模式

其目的是首先区分集成电路(IC)某一点上的逻辑电平,其次确定此时电信号的时间演化。频闪观测法似乎是获得这些结果的最佳方法。

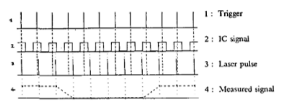

在这种方法中,激光是平稳的,而IC信号和激光脉冲之间的相位是可变的。在某一相位采集一个或多个样品后,该激光脉冲被延迟少量,因此允许在不同的相位测量该信号。(图11)

相对于波形中的某个参考点,每个样本都是在一个逐渐延迟的时间以等增量进行采集的。在这种模式的实现中有两个要点:需要产生激光脉冲和对检测到的信号进行处理(图12)。

图10

声光调制器的控制信号与随频率增加的激光脉冲之间的去相。为了使两个信号同步,必须处理这个延迟。所检测到的信号是来自芯片的反射信号,并对这个信号进行处理以获得实际波形的较慢版本。时间分辨率由时延来表示。我们用它来绘制和可视化检测到的信号,并将其与应用的IC信号进行比较。

图11 频闪模式的原理

激光脉冲宽度等于时间分辨率,而延迟变化的速率或平均值的个数决定了电压分辨率。利用这种方法,我们希望能将IC的信号可视化到最大值为300 kHz,并能区分IC的逻辑电平,最大值为3 mHz。频率限制是由于声光调制器(14mhz)的频率限制和LCs的响应时间。

向列

向列相在失效分析中是很常见的,通常用于热点的检测和用黑白图像显示芯片表面的电场。我们在IBM COMPEC实验室的研究结果允许我们在平面方向上使用介电各向异性大于0的列线图来进行可视化。在彩色显示和分辨率方面取得了良好的效果。这一点是非常重要的,因为这是第一次可以获得彩色成像与N相位。但由于这些LC响应时间较慢(1 ms),该应用程序只能在非常短的时间内被利用在低频或平均电场中观察。在配准阶段,由于使用的纯物质相变快,会出现一些缺陷,但采用大温度范围的新型混合物可以解决这一问题。

结论

使用SC的液晶的最大优点,不仅仅是颜色,是这种相位的响应时间性能。SC的可以有一个开关- ing时间约ps为1毫秒n .

这种方法的优点是彩色照片的pro -沉,光学显微镜的使用,测试是在大气con -条件,易于设置和操作,最后使用的低成本的设备。

在失效分析实验室中,它可以作为电子束流测试中通常采用的电压对比测试的另一种选择。这种方法已经成功地在16K x 4,64k SRAMs和64K, 256K dram上进行了充分的测试。

此外,在电路的一个节点上进行测量以获得内部信号的可能性似乎很大。为此,我们将实现第一个“光学振荡示波器”。此外,在电路的一个节点上进行测量以获得内部信号的可能性似乎很大。对于这样的一个应用,我们将实现第一个“光学振荡示波器”。

转载请注明精川材料检测地址:www.jctest.vip